近日,美國康奈爾大學教授艾莉莎·阿普塞爾(Alyssa Apsel)和團隊提出一種微波神經網絡(MNN,microwave neural network),其采用標準的互補金屬氧化物半導體(CMOS,Complementary Metal-Oxide-Semiconductor)技術制造,在芯片上僅占據 0.088 平方毫米的超緊湊尺寸,可支持集成到通用模擬處理器中,并且能夠完全集成在硅基微芯片上。它可以為無線電信號解碼、雷達目標跟蹤和數字數據處理等任務執行實時頻域計算,而且功耗不到 200 毫瓦。

圖 | 美國康奈爾大學教授艾莉莎·阿普塞爾(Alyssa Apsel)(來源:https://www.engineering.cornell.edu/people/alyssa-b-apsel/)

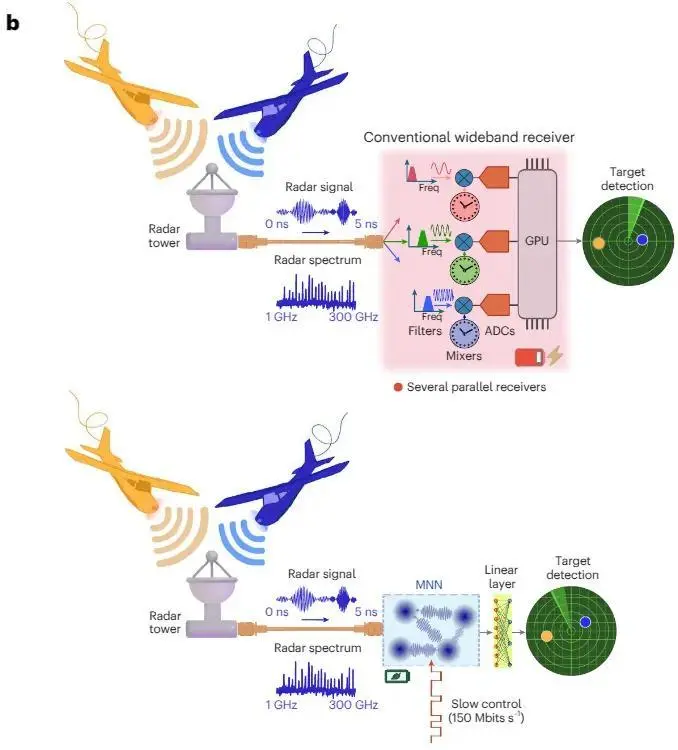

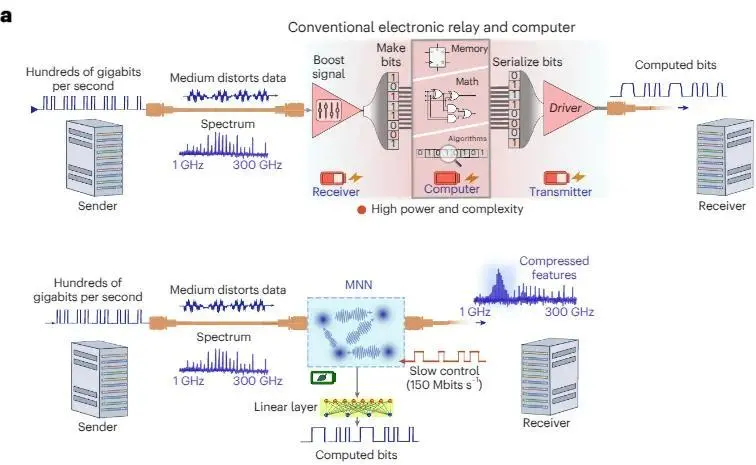

當施加低頻參數調制的時候能夠改變微波神經網絡的響應,這種可重新編程、特征豐富的頻譜,非常適合用于機器學習推理任務。該方法能在寬帶信號的整個帶寬(數千兆赫寬)內實現瞬時模擬計算,據研究人員所知,這是業內首次在集成電子設備中展示此類能力,這意味著一種新型高速計算方法的正式面世,相關論文于近期發表在 Nature Electronics(IF 40.9)。

圖 | 研究人員將這款低功耗微芯片稱為“微波大腦”,它是首款通過利用微波物理特性,同時對超高速數據信號和無線通信信號進行計算的處理器。(來源:資料圖)

01

在芯片上構建首個“微波大腦”

基于微波神經網絡,研究人員在芯片上構建了首個“微波大腦”,這是一種低功耗的微芯片,也是首款利用微波物理特性從而能夠同時針對超高速數據信號和無線通信信號進行計算的芯片。

圖 | 相關論文(來源:Nature Electronics)

該款芯片既能執行低級邏輯功能,也能完成復雜任務,例如能夠識別高速數據中的比特序列或統計二進制值。在涉及無線信號類型的多項分類任務中,它的準確率不低于 88%,能與數字神經網絡的準確率相媲美,但是功耗和尺寸僅有后者的一小部分。

在研究人員所打造的首個原型樣品中,他們證明微波神經網絡能夠替代射頻和微波機器學習任務中大部分數字網絡,同時所消耗的功率得到大幅降低,能夠擺脫高時鐘速度帶來的負擔。需要說明的是,時鐘速度是電子設備中核心工作節奏的基準參數,通常以赫茲(Hz)為單位來表示每秒執行的周期數,較高的時鐘速度會拖慢數字系統并使其發熱。有趣的是,這款芯片還能模擬數字功能,從而能夠替代冗長的時序邏輯信號鏈。

(來源:Nature Electronics)

這款芯片背后的電路拓撲結構,是論文第一作者巴拉?戈文德(Bala Govind)在康奈爾大學讀大二和大三期間,經過數月思考逐漸形成的。他在康奈爾大學官網的報道中表示,在校園山坡的多次散步中,他完成了上述結構的構思。

圖 | 論文第一作者巴拉?戈文德(Bala Govind)(來源:https://www.linkedin.com/in/bal-govind-6840979b/)

毫無疑問,微波神經網絡是本次成果得以順利完成的重中之重,那么它到底是如何誕生的?

02

微波神經網絡是如何工作的?

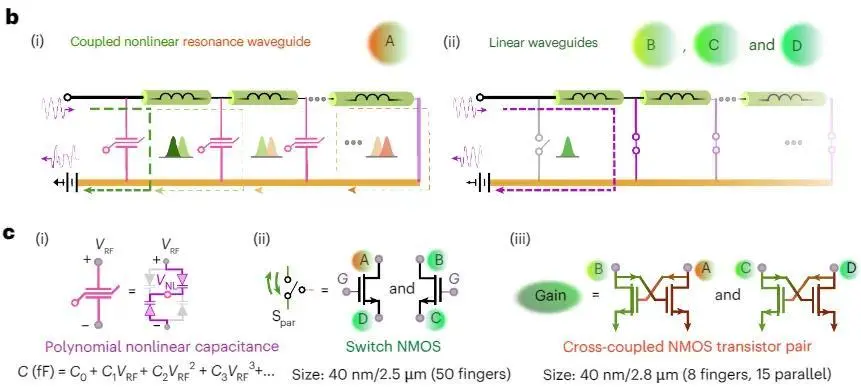

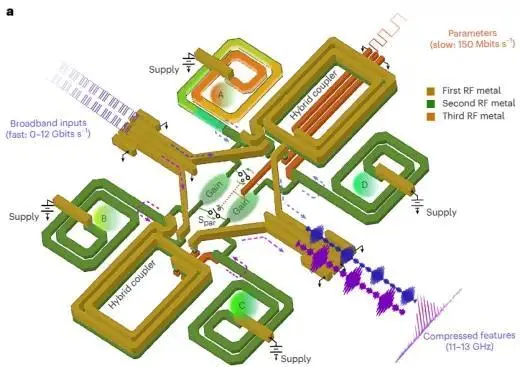

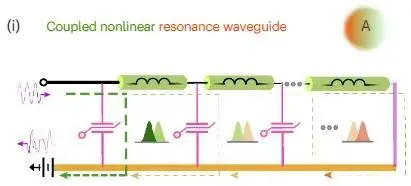

據了解,微波神經網絡是一個非線性系統,它通過產生類似梳狀、對輸入敏感的頻譜來進行計算。下圖展示了產生這一頻譜的電磁結構,該結構由一條非線性波導(標記為 A)和三條線性波導(標記為 B、C 和 D)組成。非線性波導的頻率模式受到輸入微波驅動信號的幅度和相位的強烈影響,而線性波導的模式則基本不受這些信號的影響。

(來源:Nature Electronics)

研究中,研究人員通過采用“地-信號-地-信號-地”(GSGSG,Ground–signal–ground–signal–ground)結構的波導,將吉赫茲速率的信號注入該系統。然后,構建于兩層重疊金屬之上的微型正交混合耦合器,將這些輸入信號進行功率分配,并將其引導至不同的波導中。這些被分割的小部分驅動信號隨后會在波導中反射,并在耦合器的輸出端口疊加,再通過另一組 GSGSG 波導提取出來。

如下圖所示,輸入敏感性的主要來源是波導 A 內一系列耦合的非線性諧振器,這些諧振器由電感段與非線性電容組合而成。

(來源:Nature Electronics)

研究過程中,研究人員使用了反并聯二極管,這是因為它們能夠產生具有多項式非線性的電容,而其非線性程度則取決于所施加的偏置電壓以及微波信號的強度。

在論文中,研究人員還展示了非線性波導的扭結狀態布局,當沿著其長度進行周期性地安裝開關,就可以延長或者縮短微波信號返回直流電源的路徑,在此期間并不會引入失真。

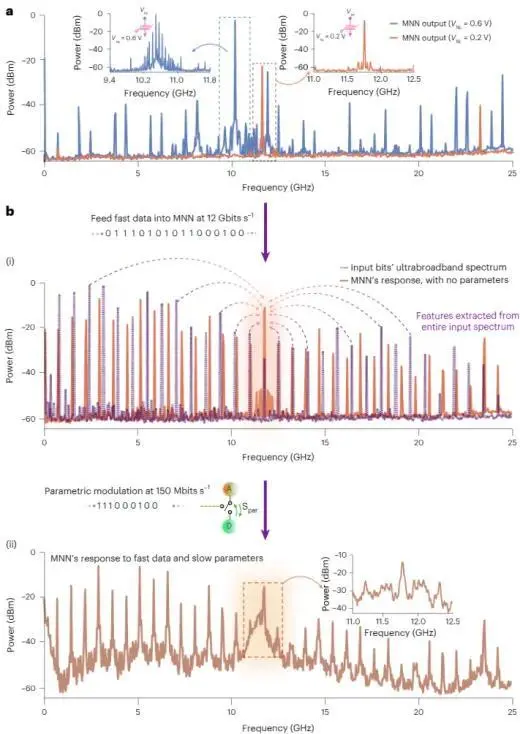

更重要的是,通過在一對波導之間連接的一對開關的開啟與關閉,研究人員建立了參數化耦合。這些開關都是 N 型金屬氧化物半導體(NMOS,N-type Metal-Oxide-Semiconductor)晶體管,并由一個比特流加以控制,該比特流的速率僅為輸入數據速率的百分之一(150Mbit/s),并通過第三條“地-信號-地”(GSG,Ground–signal–ground)波導傳輸。這種開-關交替的參數耦合序列,是針對神經網絡模式實現動態重新編程的關鍵,這使其能夠針對不同計算任務進行配置,從而與其他循環神經網絡訓練方法有著本質區別。

(來源:Nature Electronics)

而為了在數十吉赫茲的高頻下維持由高幅度微波傳輸引起的非線性,研究人員通過交叉耦合的晶體管實現了再生性的飽和增益。下圖展示了微波神經網絡的實測頻譜響應。可以看到,即使在沒有驅動信號或參數切換的情況下,其頻譜也高度依賴于振蕩器核心供電電壓以及施加在非線性電容上的偏置等因素。當接收到 12Gbit/s 的本征超寬帶數據時,其頻譜響應變得非常復雜。而微波神經網絡中的非線性,將輸入頻譜的全部特征映射到其響應最為顯著的范圍。據研究人員所知,這也是業內首次在集成 CMOS 電路中通過主動耦合非線性諧振產生微波梳狀頻譜的實例。

(來源:Nature Electronics)

研究人員進一步指出:首先,這一設計方案與傳統 CMOS 振蕩器有著較大不同,后者依賴對稱性來實現穩定的單音振蕩;其次,這一設計方案也不同于通過產生微弱諧波梳來進行光譜分析的復雜脈沖整形電路。由于研究人員旨在利用商用 CMOS 工藝實現這一模擬計算機,因此設計品質因數超過 40 的電磁結構并不現實。另據悉,克爾梳(Kerr combs)和電光頻率梳(electro-optic frequency combs)等穩定的光學頻率源,它們與混亂的外部驅動信號具有良好的隔離性。而本次研究人員在設計方案上有意讓耦合波導暴露于輸入微波之下,正是這種對于寬帶輸入的有意暴露,使得諧振器內部的非線性和非對稱性能夠實現近乎瞬時的計算。

實驗中,研究人員通過保持線性波導(B、C、D)與波導 A 的標稱振蕩頻率高度失諧,來減少物理電路參數數量。其指出,通過應用廣義耦合模理論,該系統可被描述為一組相互連接的非線性模式,其中第一個非線性模式通過慢速參數耦合和固定相位延遲與線性模式相連。與此同時,這一系統由可飽和增益供電,參數振蕩由快速微波驅動信號調制,這些信號動態不僅能夠重新配置諧振器的阻抗,并且能夠塑造系統的穩態頻譜響應。

圖 | 康奈爾大學博士生巴拉·戈文德(Bal Govind)與該校艾莉莎·阿普塞爾(Alyssa Apsel)教授合作研發出了一種首創的微波神經網絡,該網絡完全集成在硅微芯片上。它能為無線電信號解碼、雷達目標跟蹤和數字數據處理等任務執行實時頻域計算,而整個過程的功耗不到 200 毫瓦。(來源:資料圖)

研究人員指出,微波神經網絡的動力學與記憶形成的神經網絡模型具有相似性。在神經系統中,記憶存儲在穩定、重復的信息交換模式中,這些模式形成于互連的節點即神經元之間。這些吸引子網絡通過響應外部輸入而形成,并通過調整節點間的權重而產生持久模式。然而,隨著時間的推移,這些模式會從穩定的結構化行為逐漸轉變為更加混沌的狀態,從而允許多個網絡在系統中共存。當網絡從固定點吸引子過渡到混沌吸引子時,系統變得越來越隨機,導致記憶衰退并最終丟失。

研究人員發現,在本次電路中也出現了類似的從結構化狀態向更混沌狀態的轉變,并且略顯混沌的狀態可能會演化為高度混沌的模式以及完全混沌的狀態。這種演化反映了系統中記憶的存在與衰退,它的發生源于微波驅動信號與頻率調制微波參數振蕩之間的特定相互作用。這種行為也與脈沖神經網絡、基于能量的模型以及生物大腦中觀察到的連接模式高度相似。

(來源:Nature Electronics)

03

或能開發與頻段無關的神經網絡處理器

需要說明的是,本次實驗中的物理參數,比如非線性電容偏壓、諧振器頻率和可飽和增益,均保持為固定值。假如能夠動態地調整這些參數,并能采用更模擬化的參數耦合方式,而非僅僅依賴二進制比特流驅動的開關,那么將有希望提升訓練精度和驗證精度。

此外,通過使用單一線性波導替代現有的三個波導結構,可以進一步減少芯片組件數量。通過采用緊湊型的設計方案,未來還能實現互聯式頻率梳陣列的構建,從而生成更豐富的輸出頻譜,進而在壓縮帶寬內提供更多特征。這樣一來既能改進訓練數據質量,也能促進單元間的誤差校正。

盡管該芯片目前仍然處于實驗階段,但是研究人員對其可擴展性持樂觀態度。眼下,他們正在嘗試提高其準確性,并將嘗試把其集成到微波平臺和數字處理平臺中。

通過充分探索設計空間,研究人員希望能夠開發出一種與頻段無關的神經網絡處理器,通過解碼復雜的超高速數字數據以及覆蓋數百吉赫茲的毫米波信號,進而讓微波神經網絡可被用于分布式邊緣計算、智能傳感、加密、特征提取和超快速人工智能推理等領域,同時能夠減少無線和電光鏈路中高速數據互連所面臨的帶寬問題和功率開銷問題。